Description

These are the example designs for the FPGA Drive FMC adapter that allows connecting NVMe SSDs to FPGAs via the FPGA Mezzanine Card (FMC) connector.

The bare metal software application reports on the status of the PCIe link and performs enumeration of the detected PCIe end-points (ie. the SSDs). The project also contains scripts to generate PetaLinux for these platforms to allow accessing the SSDs from the Linux operating system.

PCIe IP

These designs implement a PCIe root complex to interface with the SSDs. All designs make use of the integrated PCIe blocks that are built into the FPGA or MPSoC device. The IP core that is used to exploit the integrated PCIe block depends on the device.

PCIe IP Core |

Dev boards |

|---|---|

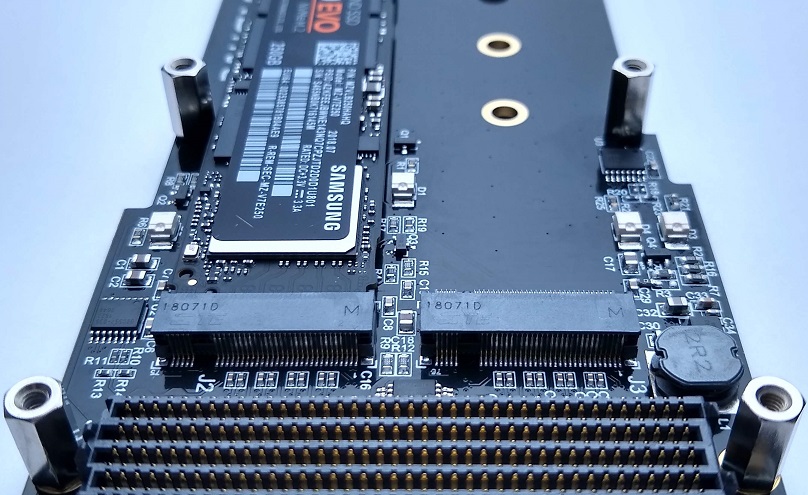

Single SSD designs

The target designs that are intended to be used with only one SSD should be loaded as shown in the above image. The SSD should be loaded into the first M.2 slot, labelled SSD1. If you are using the older version FPGA Drive FMC (Rev-B) with only one M.2 connector, you will only be able to use the single SSD designs.

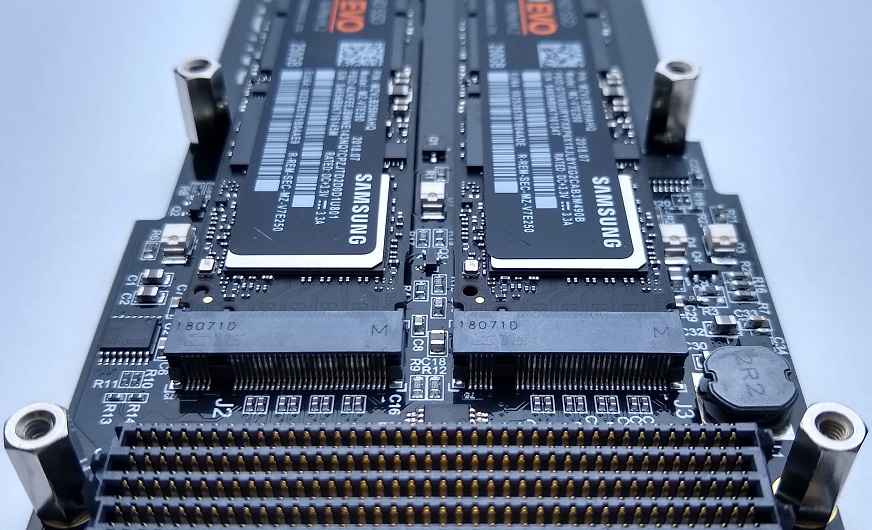

Dual SSD designs

The target designs that are intended to be used with two SSDs can be loaded as shown in the above image. The dual designs may not function as expected if only one SSD is loaded.

At the moment there are dual designs for these carriers: